TSMC nói định luật Moore vẫn chưa chết, thậm chí rất đúng với chip Bionic của Apple

Theo TSMC - hãng sản xuất bán dẫn lớn nhất thế giới nói rằng định luật Moore mà Intel theo đuổi lâu nay không hẳn đã chết mà ngược lại, nó rất đúng khi xét đến dòng vi xử lý Bionic của Apple.

Nhắc lại về định luật Moore, nó được đưa ra bởi đồng sáng lập kiêm giám đốc điều hành Intel - Gordon Moore vào năm 1965 trong đó ông nói rằng số lượng bán dẫn hay mật độ bán dẫn trên chip sẽ tăng gấp đôi mỗi năm, sau đó ông sửa lại là tăng gấp đôi mỗi 2 năm. Định luật này từng rất đúng trong giai đoạn những năm cuối thập niên 90, đầu 2000 nhưng đến hiện tại không còn chính xác nữa.

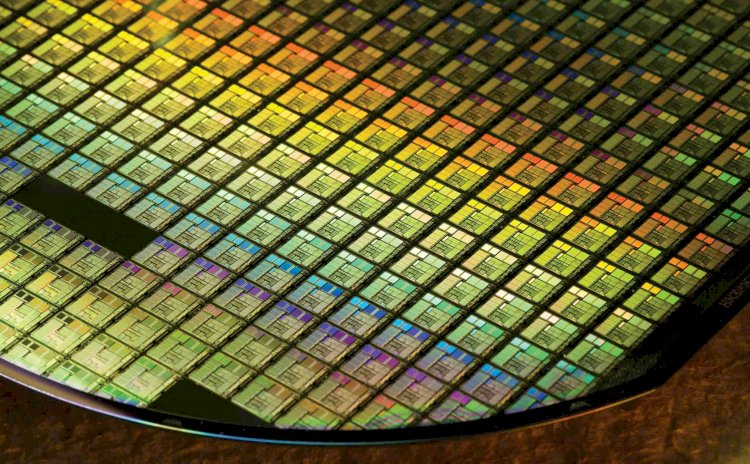

Bản thân Intel - công ty áp dụng định luật Moore để phát triển CPU đã buộc phải chuyển sang chu kỳ Tick-Tock rồi dài hơn là PAO (Process-Architecture-Optimization) và hiện hãng chỉ mới tung ra những vi xử lý dùng tiến trình 10 nm đầu tiên, trễ hẹn 3 năm so với kế hoạch ban đầu là 2016. Các hãng sản xuất bán dẫn khác cũng đang đối mặt với nhiều khó khăn trong việc thu nhỏ tiến trình, chi phí dành cho hoạt động này quá cao, chưa kể là các vấn đề như nguyên vật liệu và tình trạng sản lượng bán dẫn đạt chuẩn thấp hơn do tiến trình nhỏ.

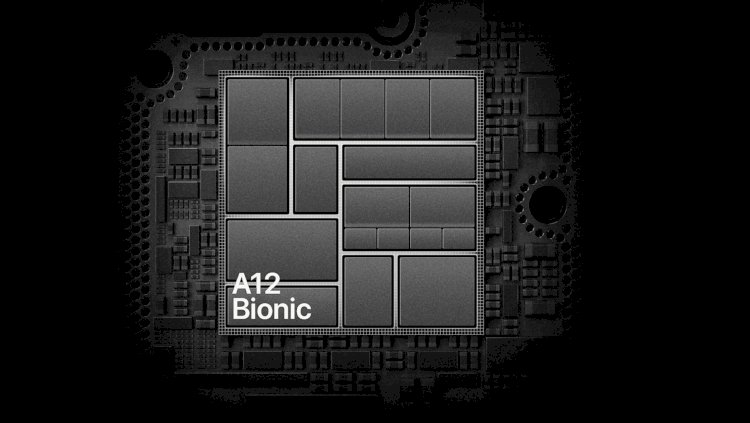

Thế nhưng định luật này lại đúng với dòng chip Bionic của Apple. TSMC nói trên trang blog chính thức rằng "định luật Moore vẫn chưa chết", giám đốc marketing toàn cầu Godfrey Cheng của TSMC nói: "Kể từ những năm 2000, hiệu năng của máy tính đã tăng mạnh không chỉ là sự cải tiến về xung nhịp mà còn bao gồm cả sự đổi mới về kiến trúc, khả năng xử lý phân luồng và xử lý song song." Theo Cheng, hiệu năng tăng cao không phải là nhờ xung nhịp tăng mà đúng ra là sự gia tăng mật độ bán dẫn - điều này khớp với định luật Moore.

Cheng nói rằng vào năm 2021 thì TSMC sẽ công bố tiến trình N5P - cải tiến cho node tiến trình N5 5 nm, hiệu năng cao hơn 7%. Những con chip Bionic A hiện tại của Apple sử dụng tiến trình 7 nm của TSMC nhưng khả năng vào năm tới, Apple sẽ sản xuất dòng Bionic A14 cho iPhone với tiến trình 5 nm.

Tuy nhiên mật độ bán dẫn chỉ là một khía cạnh cải tiến hiệu năng, một hạn chế lớn cần giải quyết là bộ nhớ đệm. Việc đặt bộ nhớ đệm gần các nhân hơn sẽ giúp giảm độ trễ đáng kể và TSMC tự tin vào các kỹ thuật đóng gói (packaging) tiên tiến của mình khi nói "có thể tích hợp các nhân xử lý logic với bộ nhớ sát với nhau". TSMC còn sở hữu công nghệ sản xuất dạng chiplet cho phép xếp chồng các chip hay wafer chồng wafer để tăng mật độ trước khi tiến hành tích hợp các thành phần khác.

Cheng một lần nữa nhấn mạnh "định luật Moore nói về việc tăng mật độ bán dẫn. Ngoài việc đạt được mật độ bán dẫn cao ở cấp độ hệ thống nhờ công nghệ đóng gói tiên tiến thì TSMC sẽ tiếp tục tìm cách tăng mật độ ở cấp độ bán dẫn. Có rất nhiều hướng để TSMC có thể cải thiện mật độ trong tương lai." TSMC tiết lộ những kỹ thuật có thể giúp tăng mật độ ở cấp độ bán dẫn có thể là "sử dụng các vật liệu 2 chiều thay vì chỉ dùng silicon làm kênh dẫn như cách truyền thống" hay "sắp xếp bán dẫn như bảng tuần hoàn hóa học", "kỹ thuật tích hợp mạch 3D cho phép CPU nằm trên GPU với các lớp bộ nhớ đặt giữa".

Theo: AppleInsider

Bạn nghĩ sao ?

thích

0

thích

0

Không thích

0

Không thích

0

Love

0

Love

0

Funny

0

Funny

0

Wow

0

Wow

0

Sad

0

Sad

0

Angry

0

Angry

0

Bình Luận (0)